针对日益提高的高速ADC系统的测试和激励,泰克专门针对ADC测试和验证的复杂性,通过TLA7000逻辑分析仪和示波器无缝集成,提供了2个层面的ADC测试和分析功能。

泰克针对多路高速ADC和DAC的测试方案泰克提供的ADC方案:

针对日益提高的高速ADC系统的测试和激励,泰克专门针对ADC测试和验证的复杂性,通过TLA7000逻辑分析仪和示波器无缝集成,提供了2个层面的ADC测试和分析功能。

ADC参数的测试,重点主要在于验证ADC转换过程中的各种动态和静态特性,具体能够通过泰克TLA逻辑分析仪和DPO71254C数字荧光示波器能够提供的测试参数如下:

SNR

ENOB

SINAD

THD

SFDR

Jitter test and analysis

ADC Transient Response

ADC Over-voltage Recovery Time

多个ADC模拟输入的time skew

绝大多数静态参数

Logic Input

Logic Output

Clock Period

Clock Pulse-width High

Clock Pulse-width Low

Output Delay

多个ADC的逻辑输出time skew测试

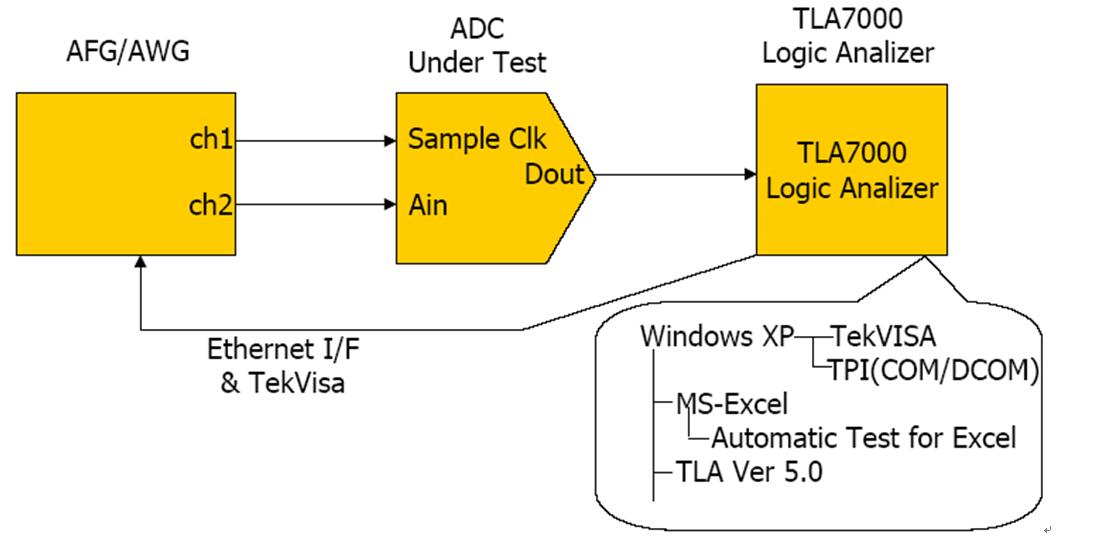

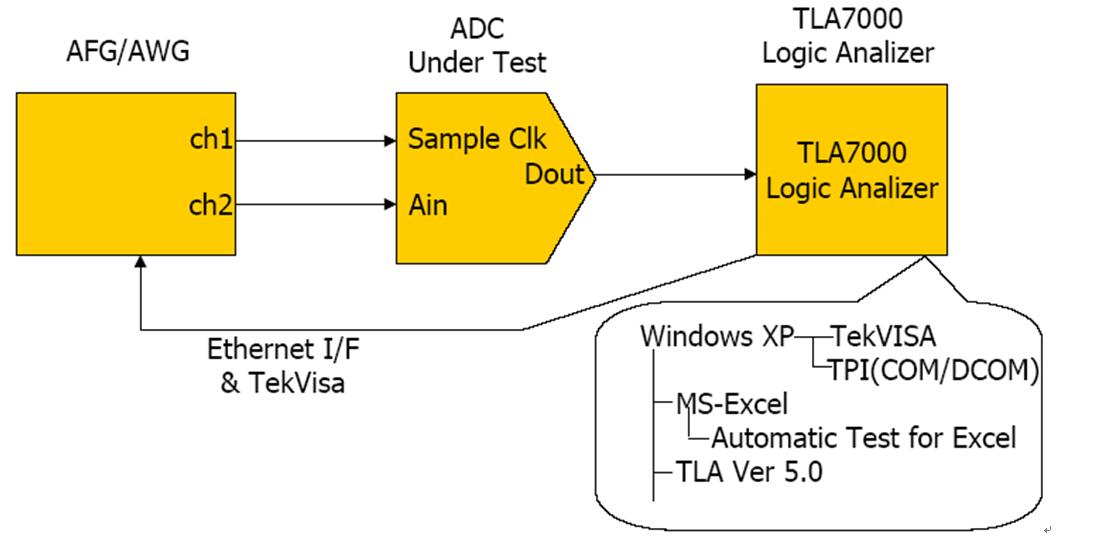

下图是ADC的测试环境:

输入信号产生和信号调理部分的验证。ADC的测试需要高精度直流电压源,点频源和宽带矢量调制源。直流源和点频源作为经典的测试工具无需进一步阐述,对当前的高速ADC系统来说,窄带/直流信号的响应并不能完全表征其性能,常常还需要给出其对宽带信号的响应特性,所以宽带/超宽带矢量调制源也会在ADC系统的测试中使用到。泰克AWG70002是一种典型的一体化超宽带矢量调制信号源,它的采样率可以达到25GS/s,最高的调制带宽可超过10GHz,使用简便,较为适合高速ADC的宽带激励。

另一方面,高速ADC系统常常包括信号调理电路、时钟电路、采样保持电路和转换电路等部分,每一部分都会对最终转化结果产生影响。在ADC系统的研发阶段,为了隔离不同部分的影响,需要使用测试设备对这些部分的输出进行测试,常用的工具包括电压表(万用表)、示波器和频谱分析仪,根据不同的激励信号选择不同的测试设备,如直流激励可用电压表测量;时钟/窄带/宽带射频激励可用频谱分析仪;而超宽带信号除了使用频谱仪观测频谱以外,还需要使用示波器这种超宽带接收机进行矢量解调验证。泰克公司在这方面都有较为完备的解决方案,包括DMM4050六位半数字万用表,RSA5106A实时频谱分析仪和DPO70000C系列数字荧光示波器配合SignalVu矢量信号分析软件组成的超宽带矢量信号分析系统。

ADC系统的验证和调试,重点主要在于对于使用ADC转换的数据进行验证分析;同时通过泰克提供的iLink工具包对每一个ADC信号提供信号完整性的测试和分析。

作为一个高速ADC采样,进而进行数据分析和处理的系统,需要高精度的时间和信号完整性测试。当系统由于时钟分配,时钟和数据PCB布线,以及ADC自身的问题时,需要合适的测试工具对故障原因进行定位和分析。 泰克TLA逻辑分析仪和DPO示波器组成系统,除了进行上述ADC参数测试外,针对设计中使用高速ADC的系统提供提供全面的测试和调试功能。例如高速ADC超过50M后,数字输出信号电特性非常关键,TLA和DPO可以精确快捷的发现各种信号完整性问题和总线故障问题,同时提供对时钟信号的分配时延和抖动提供全面的测试和分析方案。 下图是泰克示波器和逻辑分析仪组成的测试系统框图。

Communication Bus

DPO

TLA

Trigger Bus

Mux Out

该系统主要提供的功能称为 iLink工具包。它集成了两种工具的特点,将DPO数字荧光示波器(满足被测系统模拟带宽的需要)连接到逻辑分析仪。通过将模拟域和数据域的工具联合起来,提供业内唯一的iCapture探头,该探头能够观测ADC数据的模拟参数信息的同时观察相同信号的数字码流信息,这是进行全面的信号完整性分析的好方法。逻辑分析仪既可显示数字信息,又能时间相关的显示该数据的模拟波形,设计人员就可以对数字信号的模拟特性进行观察,排除系统中的错误。

ADC输出信号的测试连接

对于进行ADC之间的的输出数据的时间偏差测试;以及对于每一个ADC 的数据偏差测试,首先需要考虑的是多通道的测试连接。

为了保证对ADC信号的探测和连接,在TLA7000系列逻辑分析仪的探头前端采用有源锗化硅电路,每一个探头的输入容性负载为0.5pf,并且提供3GHz以上的模拟带宽,该探头成为iCapture探头。采用iCapture技术的有源逻辑探头,它的模拟带宽为3GHz,能够直接在测试过程中通过示波器配合来直接对ADC数字输出信号的模拟参数信息进行观测,无需在使用示波器的探头在被测电路板上寻找测试点来重复探测。这样在整个系统在只使用一套探头就能够完成逻辑和模拟的测试,整个探头的输入电容为0.5pf,保证对被测系统影响最小。

在连接方式上,逻辑分析仪探头和被测电路的连接采用压接的方式,即无需传统的为逻辑分析仪探头测试提供的测试插座或连接器。工程师在进行可测性设计时,只需要按照探头指南所提供的机械尺寸,在元件库中设计部分测试焊盘在PCB板上即可。这种无连接器方式的逻辑探头连接可以保证PCB布线测试点时产生的残桩尽可能的小,并且减小了进行可测性设计时的布线复杂度,同时提高了信号完整性。下图是泰克iCapture探测方法和传统探测方法的对比。

ADC输出信号的信号完整性测试和时间偏差测试

当需要分析ADC的输出数据时间偏差问题时,可以使用TLA7000逻辑分析仪提供的iVerify眼图测试功能,可以进行128个高速信号的眼图测试,彻底分析信号完整性问题。在 ADC数据输出中,每一路的数据和时钟的关系通过眼图显示出来,这样就能够进行时间偏差和信号完整性的分析。如下图所示。

最高 20GHz 的带宽

最高 50GS/s 的取样速率

最高 400 MB 的记录长度

4 通道

iCapture

iView

TLA逻辑分析仪

DPO示波器

逻辑分析

仪、示波

器数字测

量使用一

个探头

iVerify

3 GHz

模拟

复用器

ADC系统中时钟和数据信号的抖动测试和时间偏差测试

由于输入信号通过ADC转换为数字信号,以及进行数字处理的过程中,时钟源分配的相位和抖动非常重要。泰克示波器配合DPOJET高级抖动和时间测试软件提供了如下功能:

时钟抖动的测试和分析

时钟相位抖动的测试和分析

时钟-数据时间偏差的测试

时钟-时钟时间偏差的测试

数据-数据时间偏差的测试

泰克推荐的配置:

1台TLA7012主机配TLA7BB4超高性能逻辑分析仪模块,64M独立采集内存选件

4个P6960或P6980逻辑分析仪探头(可以直接配合示波器使用,提供3GHZ模拟带宽)

1台DPO71254C数字荧光示波器

高级定时和抖动分析软件DPOJET

高级矢量信号分析软件SignalVu

实时频谱分析仪RSA5106A

数字万用表 DMM4050

泰克提供的DAC方案

1、DAC的测试,使用主要工具是提供“D端”的激励信号和“A”端输出信号的分析。主要需要分析的项目有:

各种静态参数

各种动态参数,主要包括:

输出更新速率(工作频率)

噪声谱密度

SFDR

ACLR

输出带宽

模拟输出参数,主要包括

输出上升、下降时间

输出延时

验证输入信号能力,主要包括

输入数据对时钟信号的建立/保持时间

最大工作频率

时钟正/负占空比限制

输入信号电平幅度限制

泰克公司提供的测试方案包括任意波形发生器AWG5012C和实时频谱分析仪RSA5106A,数字荧光示波器DPO71254C,测试原理框图如下:

2、和ADC测试类似,DAC测试的一个关键点是验证DAC输出指标,此时RSA5106A实时频谱分析仪可以测试频域指标,如杂散、SFDR等,同时DPO71254C可以测试相关时域指标,如上升/下降时间等。

RSA5106A是一款操作简单,测试十分方便的频谱仪,可以快速得到各种频域指标,如下图所示的杂散测量。通过自动的杂散统计列表,用户可以立即得到SFDR等测试结果:

同样,下图是一个ACLR自动测试的例子

3、DAC测试中的另一个工具是数字信号激励。AWG5012C w/03可以提供速率最高达1200M,位宽为32bit的同步激励(差分为16路)。主要参数为:

通道数:32路单端或16路差分数据通道;

速率:10M~1200Mbps

上升时间: <300ps

每通道数据深度:16M位

输出幅度: 0.1~3.7Vpp至50欧姆,0.2~7.4Vpp至1M欧姆,分辨率为10mV

通道间时延:<400ps

在测试中,AWG5012C系统不仅可以输出理想的激励信号来测试DAC动态参数,还可以改变输出幅度以及通道间同步情况等来验证DAC的输入信号幅度和时序容限;

4、其它一些时域指标,如上升/下降时间,可以使用示波器DPO71254C。DPO71254C还可以用于AWG激励信号的验证,即在测试动态参数等之前,先用示波器观察AWG输出的信号是否已经正确配置。

5、推荐配置

AWG5012C 带03选项

RSA5106A实时频谱分析仪

DPO71254C数字荧光示波器